기술기고문

멀티옥타브 주파수 커버리지와 탁월한 위상 잡음 성능 갖춘 마이크로파 합성기 IC

마티 리처드슨(Marty Richardson), 선임 애플리케이션 엔지니어 / 아나로그디바이스(Analog Devices, Inc.)

머리말

더 높은 대역폭과 데이터 속도에 대한 요구와 함께, 시스템 주파수 및 변조 속도에 대한 요구 역시 계속해서 높아지고 있다. 여기에, 한때 군용 또는 방산 분야에서만 사용됐던 애플리케이션들이 상용 시장에서도 사용되면서 저전력 특성도 중요해졌다. 이러한 요구들을 전기적 성능이나 기능을 희생하지 않으면서 충족해야 한다는 것이 과제다. 이를 위해서는 신호대잡음비(SNR), 비트 오류율(BER), 서비스 품질(QoS) 같은 것들을 향상시켜야 하고, 로컬 오실레이터(LO)의 위상 잡음을 향상시켜야 한다. 아나로그디바이스(Analog Devices)가 새롭게 출시한 ADF5610은 위상 동기 루프(PLL)와 전압 제어 오실레이터(VCO)를 통합한 것으로서, ADI가 이러한 요구들을 충족하는 솔루션을 제공하기 위해서 얼마나 노력하고 있는지를 잘 보여준다.

주파수 커버리지

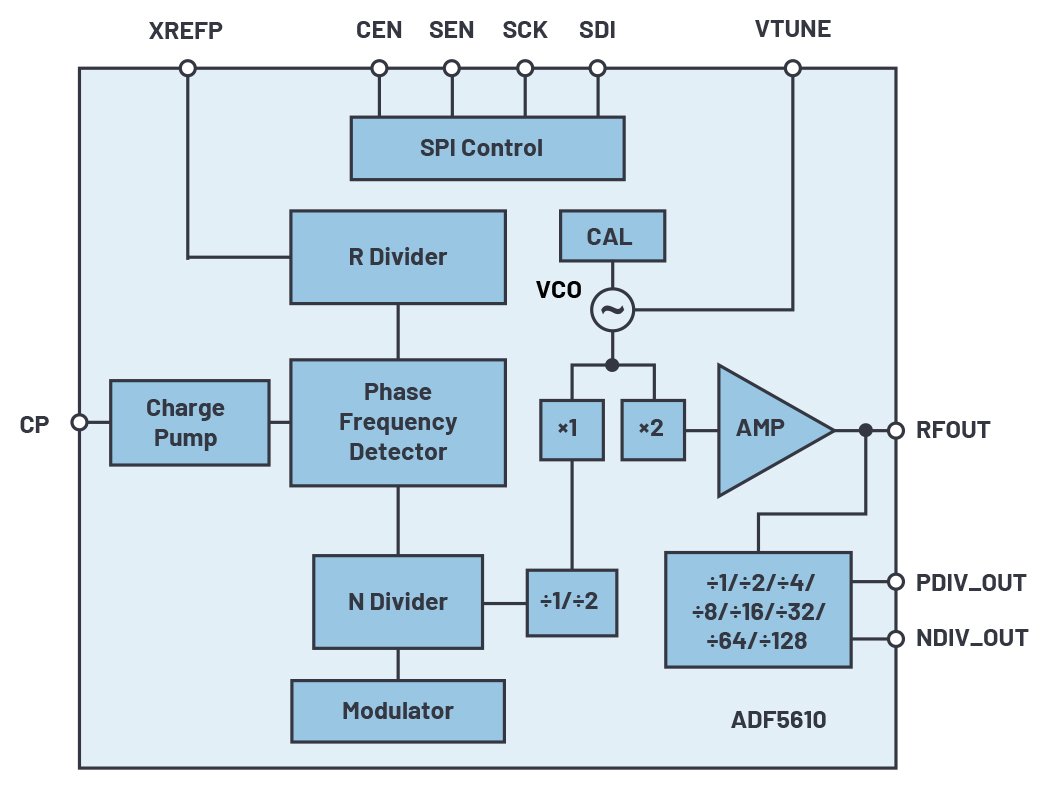

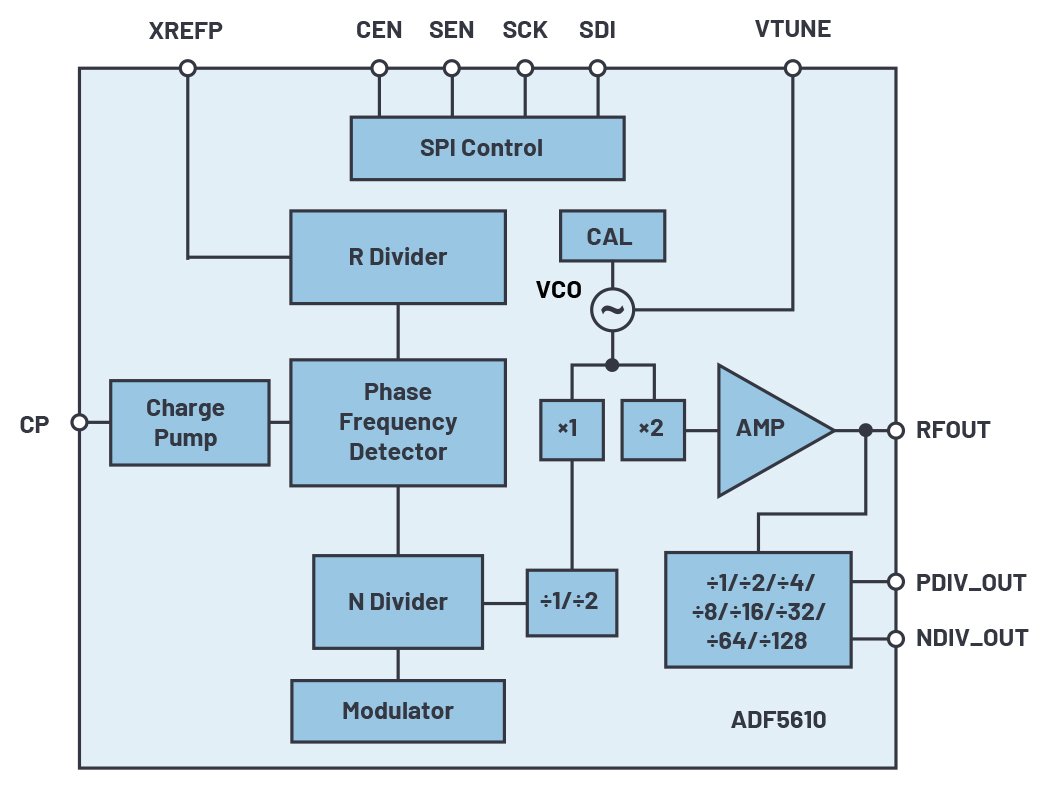

ADF5610은 총 8개 옥타브를 지원하며, VCO 기본 주파수는 3.65GHz ~ 7.3GHz이고 이것을 PLL로 전달해서 위상 잡음을 최소화한다. 싱글 엔드 출력(RFOUT)은 기본 주파수 범위를 두 배로 해서 7.3GHz ~ 14.6GHz를 제공하고, 차동 출력은 1/2/4/8/16/32/64/128 설정의 분주를 사용해서 57MHz ~ 14.6GHz의 전체 동작 범위를 지원한다.

그림 1: ADF5610의 블록 다이어그램

ADF5610의 VCO 아키텍처는 광대역 합성기 성능을 제공할 뿐 아니라, 10GHz에서 100kHz의 오프셋에서 -114dBc/Hz 공칭 개방 루프 위상 잡음의 업계 선도적인 위상 잡음 성능을 유지한다. 내부 상태기는 수동 루프 필터만을 사용해서 40µs 미만의 주파수 안정화 시간을 달성한다. 따라서 이보다 빠른 안정화 시간이 필요하지 않다면 추가적인 회로나 룩업테이블(LUT)을 사용할 필요가 없다.

컨버터 클록용으로 뛰어난 PLL 성능

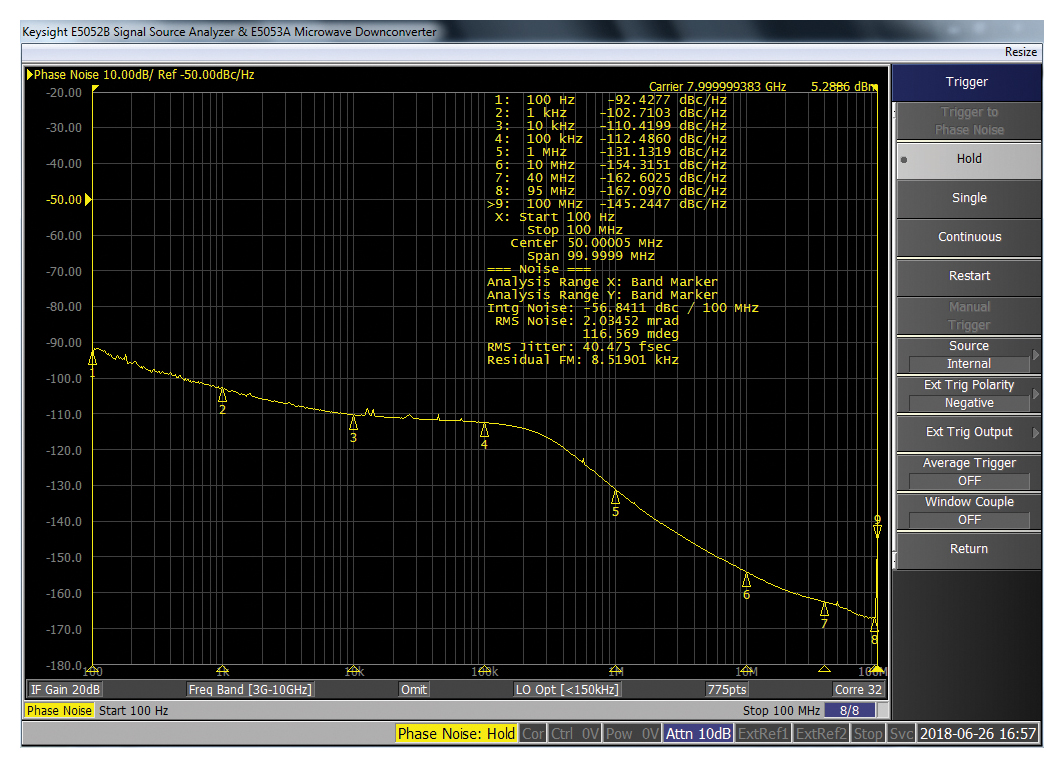

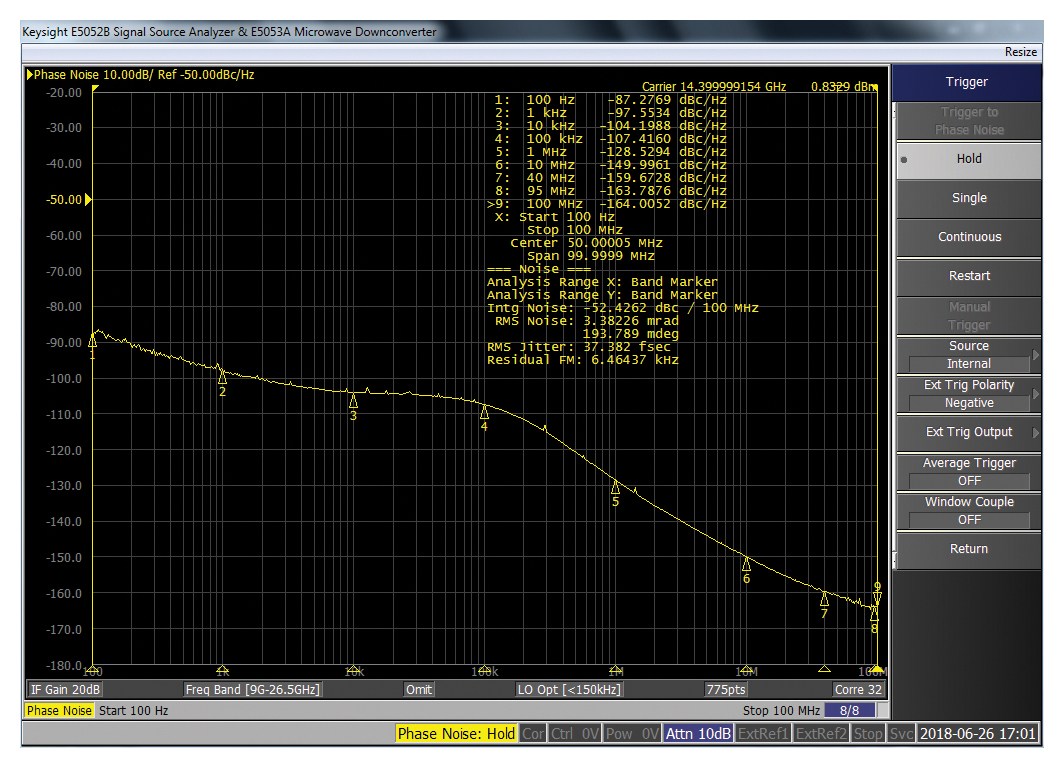

ADF5610에 통합된 PLL은 -229dBc/Hz(고전류 모드로는 -232dBc/Hz)의 평범한 FOM(figure of merit)을 나타내지만, 탁월한 1/f 잡음(-129dBc/Hz) 및 VCO 위상 잡음 특성과 결합하면 38fs 미만의 rms 지터 수치를 달성(1kHz~100MHz 적분 한계)할 수 있다. 그러므로 ADF5610은 극히 까다로운 컨버터 클록 애플리케이션에 사용하기에 적합하다. 열 잡음과 고주파(100MHz)를 낮추기 위해서는 루프 필터 저항 값을 최소한으로 유지해야 한다. 이 정도 성능 수준을 달성하려면 잡음이 극히 낮은 레퍼런스 소스가 필요하다.

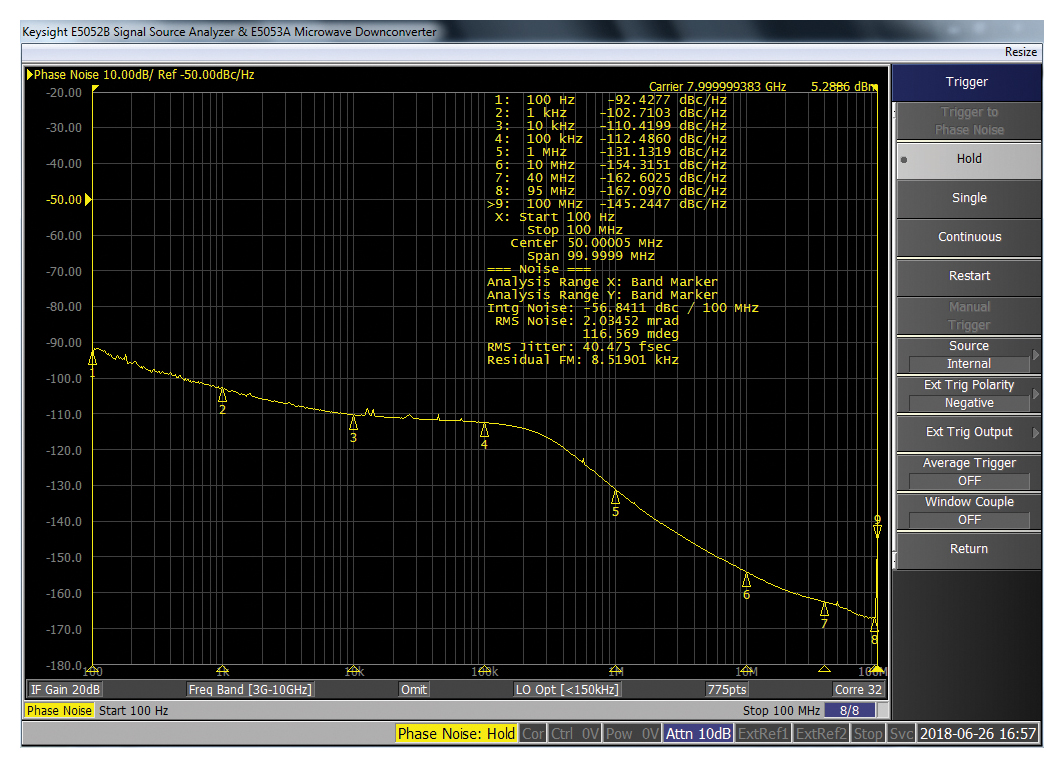

그림 2: RMS 지터: 8.0GHz

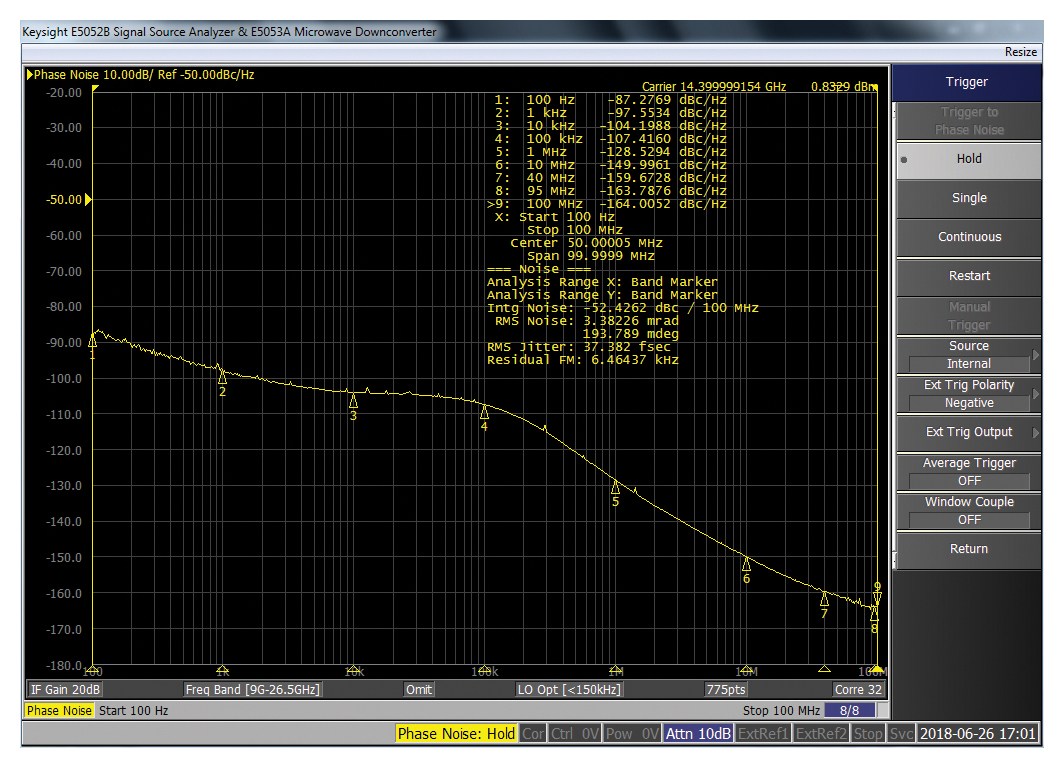

그림 3: RMS 지터: 14.4GHz

통신 및 계측 애플리케이션용 LO

넓은 주파수 커버리지, 업계 선도적인 위상 잡음, 월등히 빠른 동기 시간 외에, ADF5610은 무선통신 및 계측 애플리케이션용 LO로 사용하기에 적합한 특징들을 갖추고 있다.

분수 분해능(fractional resolution)은 24비트로 보통이지만, ADF5610의 정확한 주파수 모드 기능과 결합하면 0Hz 오차로 주파수 생성이 가능하다. ADF5610을 LO로 사용하면 출력 전력이 공칭 5dBm이기 때문에 능동 믹서를 RFOUT 포트로부터 직접 구동할 수 있다. 따라서 추가적인 증폭이 필요치 않아 귀중한 보드 공간을 절약할 수 있다. 차동 분할기(PDIVOUT/NDIVOUT)의 출력 전력은 싱글 엔드로 사용하면 공칭 2dBm인데, 협대역 애플리케이션을 위해 저손실 발룬(balun)이나 하이브리드 커플러를 통해 결합하면 출력 전력을 몇 dB 더 높이거나 2배의 출력 전력을 달성할 수 있다.

오늘날에는 저전력 특성이 중요하게 요구되는데, ADF5610은 700mW 미만(출력 분할기를 비활성화한 상태에서의 저전류 모드일 때)에서부터, 최악의 조건일 때에도 1W 조금 넘는 수준(출력 분할기를 128 분주로 설정한 상태에서의 고성능 모드일 때)밖에 소모하지 않는다는 점이 또 다른 장점이다. 저전류 모드에서도 위상 잡음 성능이 동급 제품들 중에서 가장 뛰어나 단지 2dBc/Hz밖에 증가하지 않는다. 또한 ADF5610은 스퓨리어스 성능이 우수해서, PFD 스퓨리어스가 -105dBc로 낮고 대역내 필터링하지 않은 정수 경계 스퍼는 공칭 -45dBc이다.

작은 크기

ADF5610 PLL/VCO는 7mm x 7mm 48핀 LGA(land grid array) 패키지로 제공된다. 추가적인 디커플링은 최소한으로 필요하며, 소형 풋프린트 솔루션으로서는 최고의 성능을 제공한다. 최상의 성능을 달성해야 한다면 ADM7150, LT3045/LT3042, HMC1060 같은 고품질 LDO 레귤레이터를 사용할 것을 권장한다. VCO는 5V 전원을 필요로 하고, 나머지 회로는 3.3V 레일로 구동된다. ADIsimPLL™로 ADF5610을 시뮬레이트 하면 전체 PLL 합성기를 구현하는데 필요한 적정 외부 회로를 설계할 수 있다.

맺음말

아나로그디바이스의 ADF5610은 최고의 주파수 커버리지 및 위상 잡음 성능에 높은 출력 전력과 저전력 소모 특성을 소형 폼팩터에 결합하고 있어, 설계 요건이 매우 까다로운 최신 통신 및 계측 시스템에 사용하기에 적합하다.

저자 소개

마티 리처드슨(Marty Richardson)은 2014년에 마이크로파 주파수 생성 그룹의 선임 애플리케이션 엔지니어로 아나로그디바이스(Analog Devices)에 합류했다. 35년 넘게 RF/마이크로파 분야에 종사해 왔으며, 현재는 위상 동기 루프(PLL), 전압 제어 오실레이터(VCO), 주파수 체배기 제품을 주로 맡고 있다. IEEE 시니어 멤버이며, 여가 중에는 가족과 시간을 보내고 집수리, 사냥, 낚시, 등산 같은 취미생활을 즐긴다. 문의: marty.richardson@analog.com

머리말

더 높은 대역폭과 데이터 속도에 대한 요구와 함께, 시스템 주파수 및 변조 속도에 대한 요구 역시 계속해서 높아지고 있다. 여기에, 한때 군용 또는 방산 분야에서만 사용됐던 애플리케이션들이 상용 시장에서도 사용되면서 저전력 특성도 중요해졌다. 이러한 요구들을 전기적 성능이나 기능을 희생하지 않으면서 충족해야 한다는 것이 과제다. 이를 위해서는 신호대잡음비(SNR), 비트 오류율(BER), 서비스 품질(QoS) 같은 것들을 향상시켜야 하고, 로컬 오실레이터(LO)의 위상 잡음을 향상시켜야 한다. 아나로그디바이스(Analog Devices)가 새롭게 출시한 ADF5610은 위상 동기 루프(PLL)와 전압 제어 오실레이터(VCO)를 통합한 것으로서, ADI가 이러한 요구들을 충족하는 솔루션을 제공하기 위해서 얼마나 노력하고 있는지를 잘 보여준다.

주파수 커버리지

ADF5610은 총 8개 옥타브를 지원하며, VCO 기본 주파수는 3.65GHz ~ 7.3GHz이고 이것을 PLL로 전달해서 위상 잡음을 최소화한다. 싱글 엔드 출력(RFOUT)은 기본 주파수 범위를 두 배로 해서 7.3GHz ~ 14.6GHz를 제공하고, 차동 출력은 1/2/4/8/16/32/64/128 설정의 분주를 사용해서 57MHz ~ 14.6GHz의 전체 동작 범위를 지원한다.

그림 1: ADF5610의 블록 다이어그램

ADF5610의 VCO 아키텍처는 광대역 합성기 성능을 제공할 뿐 아니라, 10GHz에서 100kHz의 오프셋에서 -114dBc/Hz 공칭 개방 루프 위상 잡음의 업계 선도적인 위상 잡음 성능을 유지한다. 내부 상태기는 수동 루프 필터만을 사용해서 40µs 미만의 주파수 안정화 시간을 달성한다. 따라서 이보다 빠른 안정화 시간이 필요하지 않다면 추가적인 회로나 룩업테이블(LUT)을 사용할 필요가 없다.

컨버터 클록용으로 뛰어난 PLL 성능

ADF5610에 통합된 PLL은 -229dBc/Hz(고전류 모드로는 -232dBc/Hz)의 평범한 FOM(figure of merit)을 나타내지만, 탁월한 1/f 잡음(-129dBc/Hz) 및 VCO 위상 잡음 특성과 결합하면 38fs 미만의 rms 지터 수치를 달성(1kHz~100MHz 적분 한계)할 수 있다. 그러므로 ADF5610은 극히 까다로운 컨버터 클록 애플리케이션에 사용하기에 적합하다. 열 잡음과 고주파(100MHz)를 낮추기 위해서는 루프 필터 저항 값을 최소한으로 유지해야 한다. 이 정도 성능 수준을 달성하려면 잡음이 극히 낮은 레퍼런스 소스가 필요하다.

그림 2: RMS 지터: 8.0GHz

그림 3: RMS 지터: 14.4GHz

통신 및 계측 애플리케이션용 LO

넓은 주파수 커버리지, 업계 선도적인 위상 잡음, 월등히 빠른 동기 시간 외에, ADF5610은 무선통신 및 계측 애플리케이션용 LO로 사용하기에 적합한 특징들을 갖추고 있다.

분수 분해능(fractional resolution)은 24비트로 보통이지만, ADF5610의 정확한 주파수 모드 기능과 결합하면 0Hz 오차로 주파수 생성이 가능하다. ADF5610을 LO로 사용하면 출력 전력이 공칭 5dBm이기 때문에 능동 믹서를 RFOUT 포트로부터 직접 구동할 수 있다. 따라서 추가적인 증폭이 필요치 않아 귀중한 보드 공간을 절약할 수 있다. 차동 분할기(PDIVOUT/NDIVOUT)의 출력 전력은 싱글 엔드로 사용하면 공칭 2dBm인데, 협대역 애플리케이션을 위해 저손실 발룬(balun)이나 하이브리드 커플러를 통해 결합하면 출력 전력을 몇 dB 더 높이거나 2배의 출력 전력을 달성할 수 있다.

오늘날에는 저전력 특성이 중요하게 요구되는데, ADF5610은 700mW 미만(출력 분할기를 비활성화한 상태에서의 저전류 모드일 때)에서부터, 최악의 조건일 때에도 1W 조금 넘는 수준(출력 분할기를 128 분주로 설정한 상태에서의 고성능 모드일 때)밖에 소모하지 않는다는 점이 또 다른 장점이다. 저전류 모드에서도 위상 잡음 성능이 동급 제품들 중에서 가장 뛰어나 단지 2dBc/Hz밖에 증가하지 않는다. 또한 ADF5610은 스퓨리어스 성능이 우수해서, PFD 스퓨리어스가 -105dBc로 낮고 대역내 필터링하지 않은 정수 경계 스퍼는 공칭 -45dBc이다.

작은 크기

ADF5610 PLL/VCO는 7mm x 7mm 48핀 LGA(land grid array) 패키지로 제공된다. 추가적인 디커플링은 최소한으로 필요하며, 소형 풋프린트 솔루션으로서는 최고의 성능을 제공한다. 최상의 성능을 달성해야 한다면 ADM7150, LT3045/LT3042, HMC1060 같은 고품질 LDO 레귤레이터를 사용할 것을 권장한다. VCO는 5V 전원을 필요로 하고, 나머지 회로는 3.3V 레일로 구동된다. ADIsimPLL™로 ADF5610을 시뮬레이트 하면 전체 PLL 합성기를 구현하는데 필요한 적정 외부 회로를 설계할 수 있다.

맺음말

아나로그디바이스의 ADF5610은 최고의 주파수 커버리지 및 위상 잡음 성능에 높은 출력 전력과 저전력 소모 특성을 소형 폼팩터에 결합하고 있어, 설계 요건이 매우 까다로운 최신 통신 및 계측 시스템에 사용하기에 적합하다.

저자 소개

마티 리처드슨(Marty Richardson)은 2014년에 마이크로파 주파수 생성 그룹의 선임 애플리케이션 엔지니어로 아나로그디바이스(Analog Devices)에 합류했다. 35년 넘게 RF/마이크로파 분야에 종사해 왔으며, 현재는 위상 동기 루프(PLL), 전압 제어 오실레이터(VCO), 주파수 체배기 제품을 주로 맡고 있다. IEEE 시니어 멤버이며, 여가 중에는 가족과 시간을 보내고 집수리, 사냥, 낚시, 등산 같은 취미생활을 즐긴다. 문의: marty.richardson@analog.com

제품스펙